В ходе конференции IEDM компания TSMC раскатала интересную дорожную карту. Казалось бы, ну каких планов на будущее можно ждать от контрактного чипмейкера, кроме более тонких техпроцессов? В целом, на это «роадмап» и направлен, но в разрезе не просто нанометров, а транзисторных бюджетов.

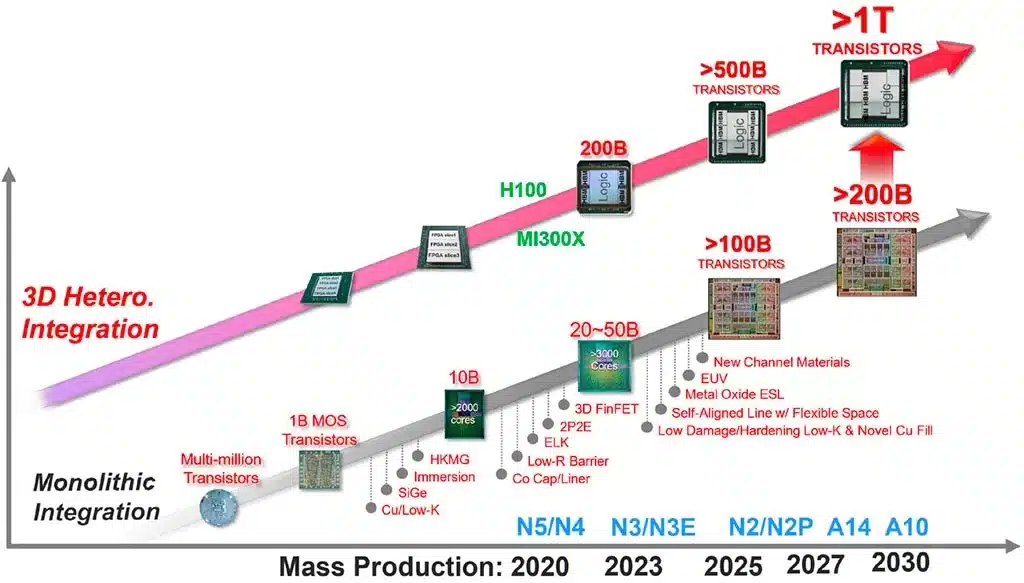

В ближайшую 7-летку TSMC планирует освоить техпроцессы N2, N2P, А14, и к 2023 году А10 (А – ангстрем, это 1/10 нанометра). При этом транзисторные бюджеты вырастут несоразмерно уменьшению нанометров.

Компания явно разделяет будущее на 2 ветви: с 3D-упаковкой, и без. Под 3D подразумевается объединение нескольких кристаллов на одной подложке. Сейчас такой подход используется в ускорителях NVIDIA, AMD, и Intel. Рекорд по части транзисторного бюджета принадлежит Intel Ponte Vecchio – 100 млрд в 47 отдельных кристаллах. К 2030 году TSMC собирается увеличить этот показатель в 10 раз.

Что касается монолитных кристаллов, сейчас рекордсмен – графический процессор AD102 в составе RTX 4090 – 76,3 млрд. В 2026 эта цифра будет почти нормой, а к 2030 один чип сможет вместить свыше 200 млрд транзисторов.

Источники:

Tom’s Hardware

Techpowerup