В прошлом году производители NAND-микросхем памяти начали массовый выпуск памяти типа QLC, где на одну ячейку приходится 4 бита информации. Казалось бы, на ближайшие несколько лет дальнейший вектор развития ёмкости NAND определен, и он заключается в наращивании количества слоёв. Но на конференции Flash Memory Summit 2019 компании Toshiba и Western Digital поведали о планах выпуска микросхем типа PLC (Penta Level Cell) с пятью битами памяти на ячейку.

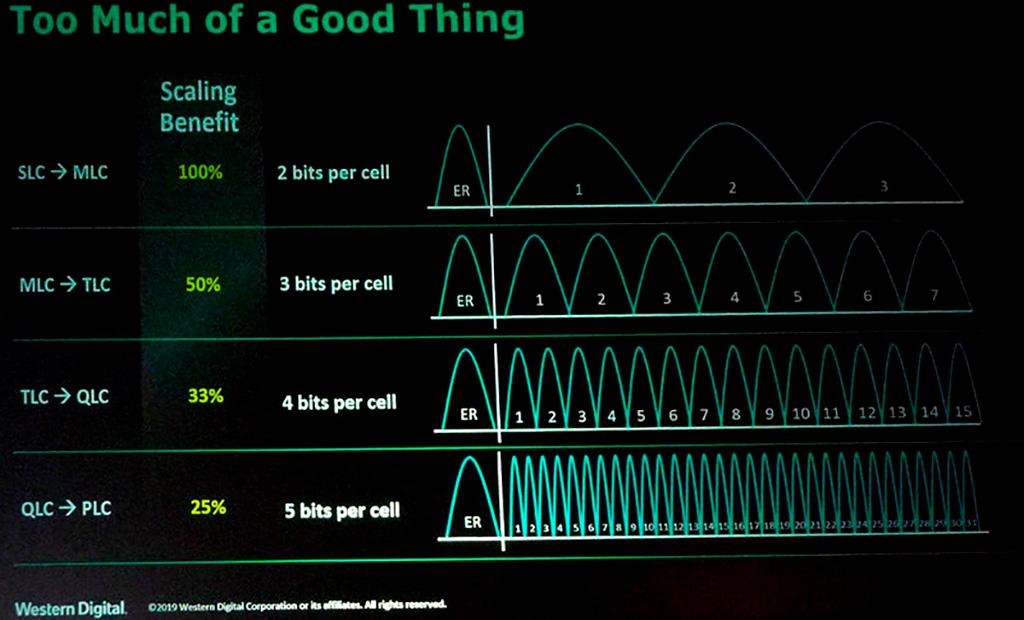

Уплотнение дополнительного бита информации сразу же увеличивает ёмкость микросхем на 25% по сравнению с QLC, однако от этого появляется целый ряд проблем. Скорости работы PLC-памяти будут очень низкими, как и ресурс записи. Кроме того, использование SLC-кэширования крайне пагубно скажется на и без того маленьком ресурсе.

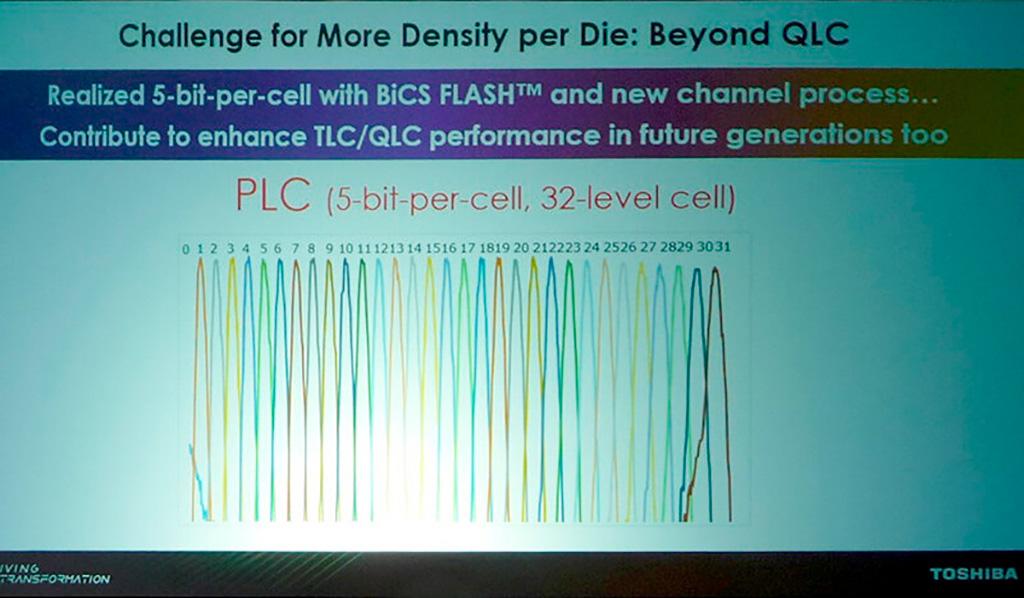

Для записи 5 бит потребуется уже 32 уровня сигнала. Таким образом, процесс хранения становится намного сложнее и более подвержен ошибкам, чем в QLC-NAND. Чем больше уровней сигнала нужно различать – тем больше вероятность ошибок, и тем больше требуется кода коррекции.

PLC-память найдёт применение в областях, где операции записи редкое явление. Предположительно, это будут накопители типа WORM (Write-Once Read Many) – записанные однократно.

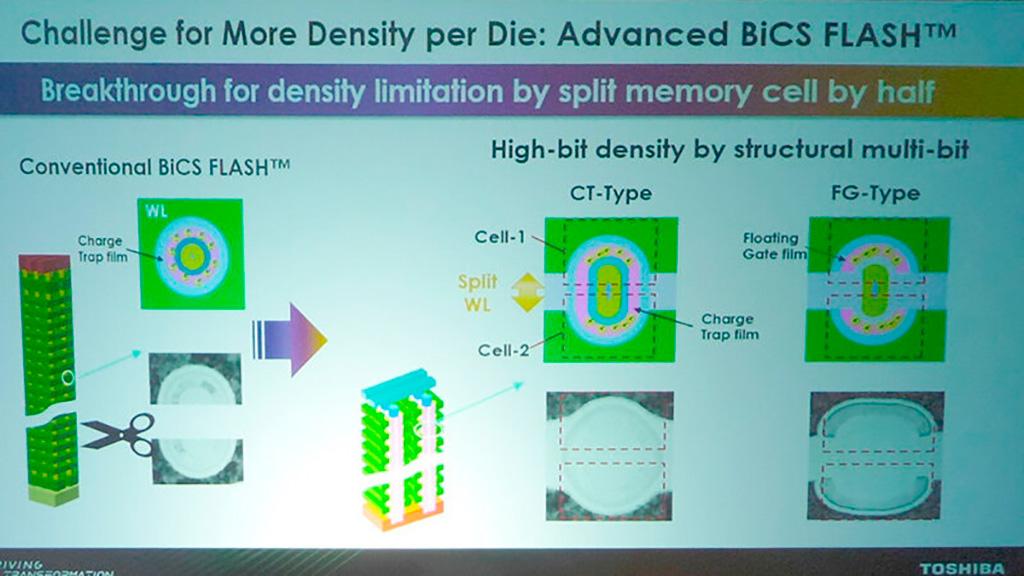

Отдельно стоит упомянуть про Toshiba и её новую концепцию разделения бита памяти пополам. Согласно отчёту, это должно эффективно удвоить плотность хранения, но до конца не понятно, как это будет работать, и реализуемо ли вообще. С таким подходом 4-битная память QLC может превратиться в 8-битную.

Источник:

ComputerBase