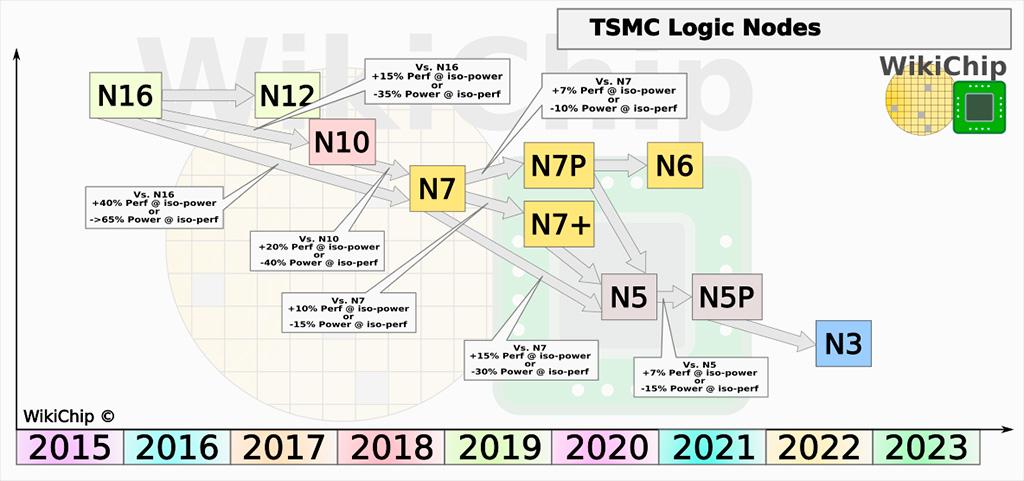

После того, как TSMC добилась высокого показателя выхода годной продукции по 7-нм техпроцессу, и даже по доработанным 7 нм, следующей важной вехой является освоение 5-нм техпроцесса. В начале этого года TSMC уже начала пробное производство по технологии N5 (по сути, 5 нм) с планами приступить к массовому производству в апреле-мае. К концу года, если коронавирус не поломает все планы, TSMC будет готова производить чипы по улучшенным 5 нм – N5P.

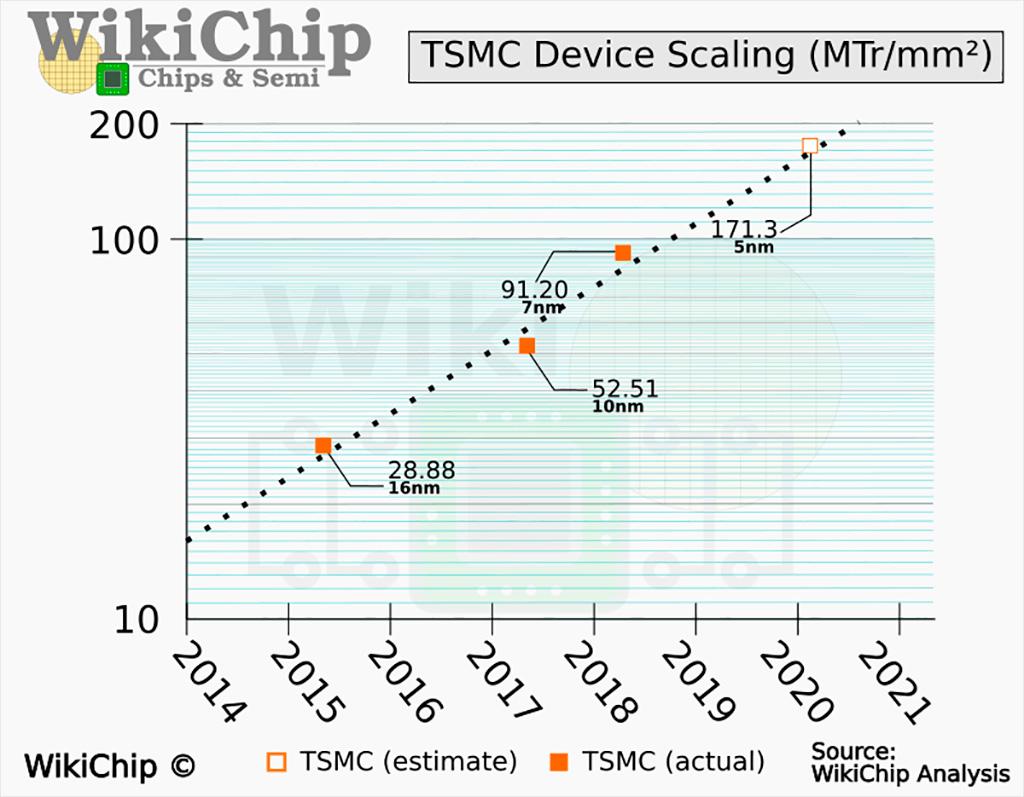

Согласно анализу WikiChip, узел N5P увеличит плотность размещения транзисторов на 87% по сравнению с первой итерацией 7-нм техпроцесса (N7). Сама TSMC оценивает показатель роста плотности размещения несколько скромнее – на 84%.

Расчётно чипы, выполненные по техпроцессу N5P, будут иметь плотность транзисторов 171,3 млн. на см2. Для сравнения, у техпроцесса N7 этот показатель равен 91,2 млн. на см2.

Ожидается, что техпроцесс TSMC N5P будет готов к концу этого года, а первым крупным заказчиком как обычно станет Apple. На нём компания построит свои SoC серии A14.

Источники:

Techpowerup

WikiChip